# 碲锌镉探测器低噪声前端读出 芯片及数据采集系统设计

罗杰

清华大学工程物理系

# 主要内容

- ◆ CdZnTe探测器

- ◆ CASACZT16前端芯片电路设计

- ◆ CASACZT16芯片测试及噪声分析

- ◆ PDD数据采集系统

- ◆ 总结及后续工作展望

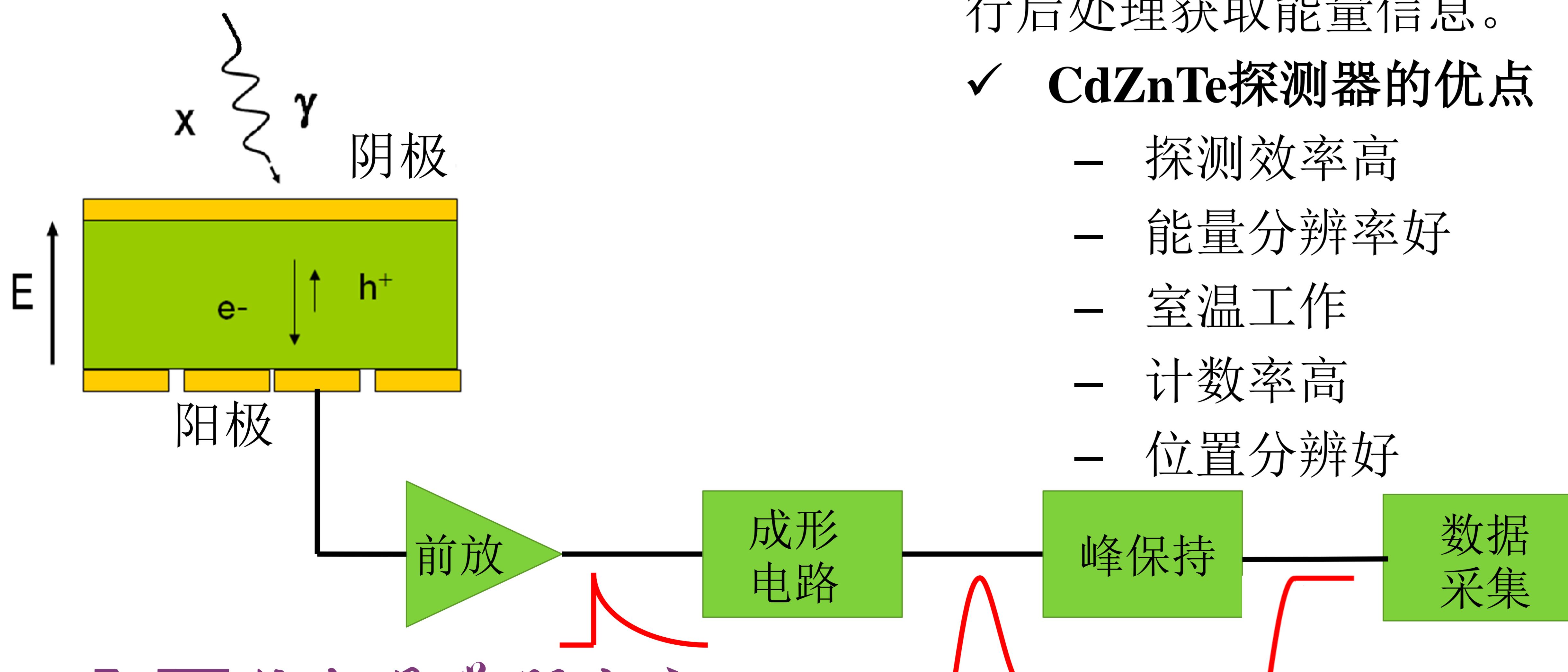

# CdZnTe探测器

## ✓ CdZnTe

- 新型的室温半导体探测器

- 可以将X或 $\gamma$ 光子直接转换为电子空穴对

## ✓ 工作原理

射线与物质相互作用产生电子空穴对，在外加电场的作用下电荷被收集并产生感应电荷，产生的电荷与射线能量成正比，信号被放大和滤波，并进行后处理获取能量信息。

## ✓ CdZnTe探测器的优点

- 探测效率高

- 能量分辨率好

- 室温工作

- 计数率高

- 位置分辨好

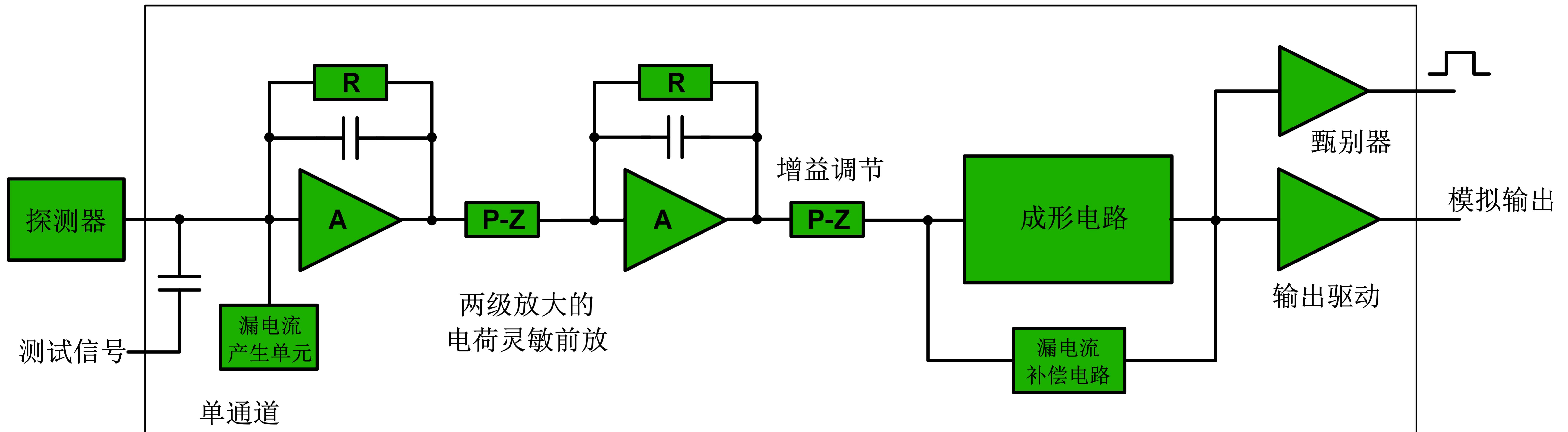

# CASACZT16原理框图

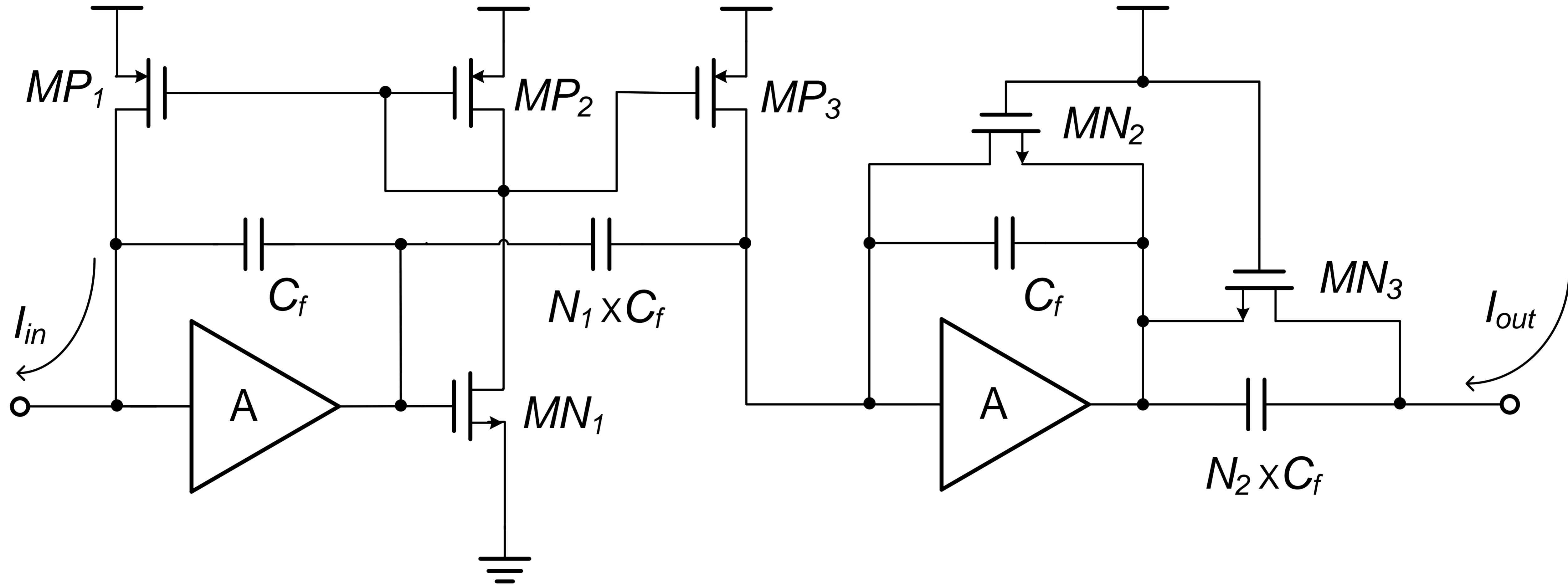

CASACZT16单通道电路图

$$V_{out} = NQ \frac{\tau/C}{(1 + s\tau)^5} \quad \tau = \lambda R C$$

- 两级放大的电荷灵敏前放，4阶半高斯成形电路，漏电流补偿电路，甄别器，输出驱动放大器，漏电流产生单元

- 电荷增益: 64~256, 通道增益: 100mV/fC~400mV/fC, 外部可调

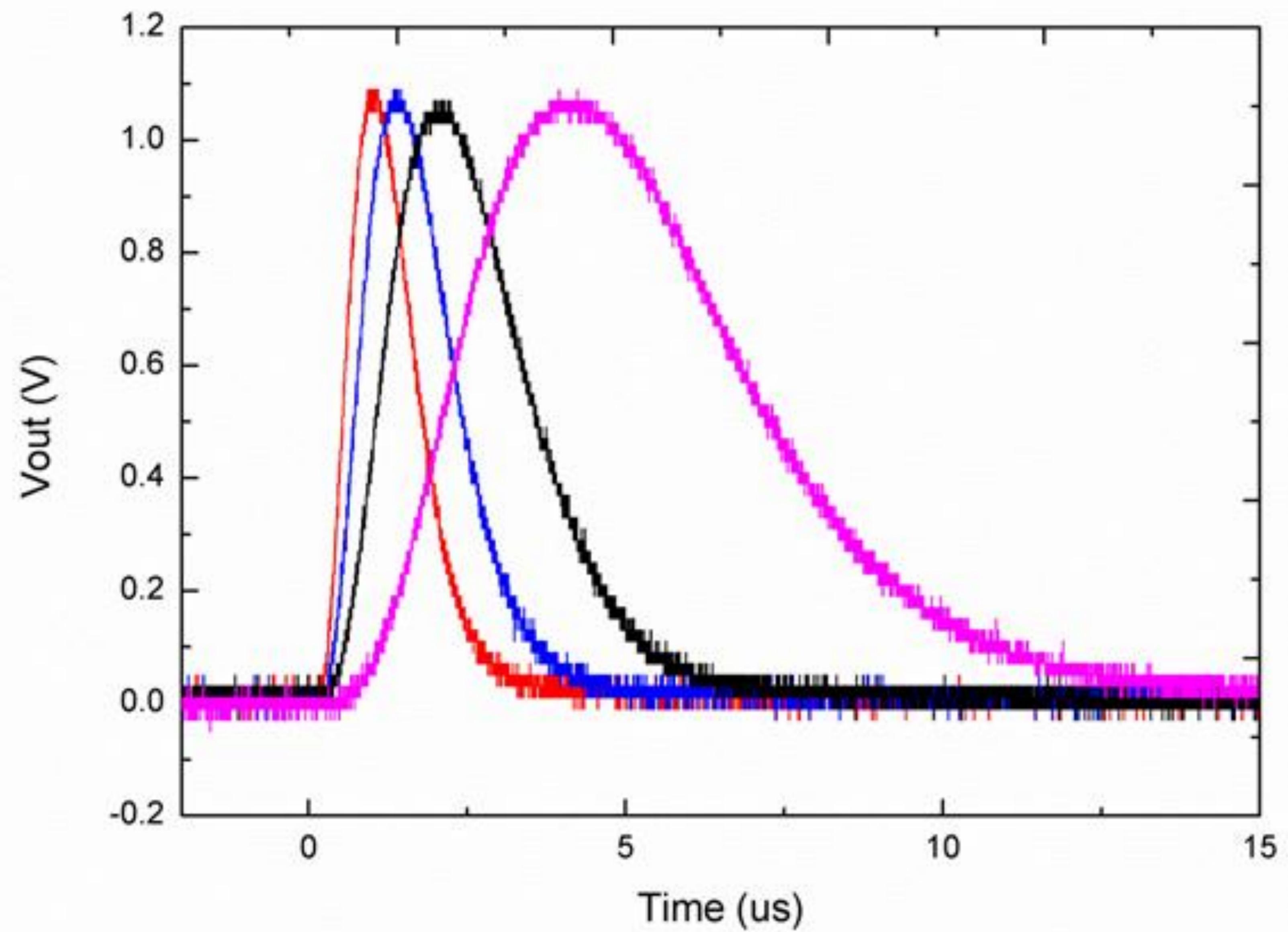

- 达峰时间: 1us~4us, 外部可调

# 两级电荷灵敏前放

两级放大的电荷灵敏前放<sup>[1]</sup>

- 电荷放大倍数:  $N_1 \times N_2$ ,  $N_1=16$ ,  $N_2=4\sim 16$

- 输入PMOS管针对5pF输入电容进行噪声优化: 尺寸为800um/0.35um, 电流为400uA, 跨导为7.1mS, 仿真ENC贡献为30e

- 反馈电容:0.125pF, 反馈MOS管: 0.4um/50um

- 前放运放采用折叠共源共栅单端运算放大器

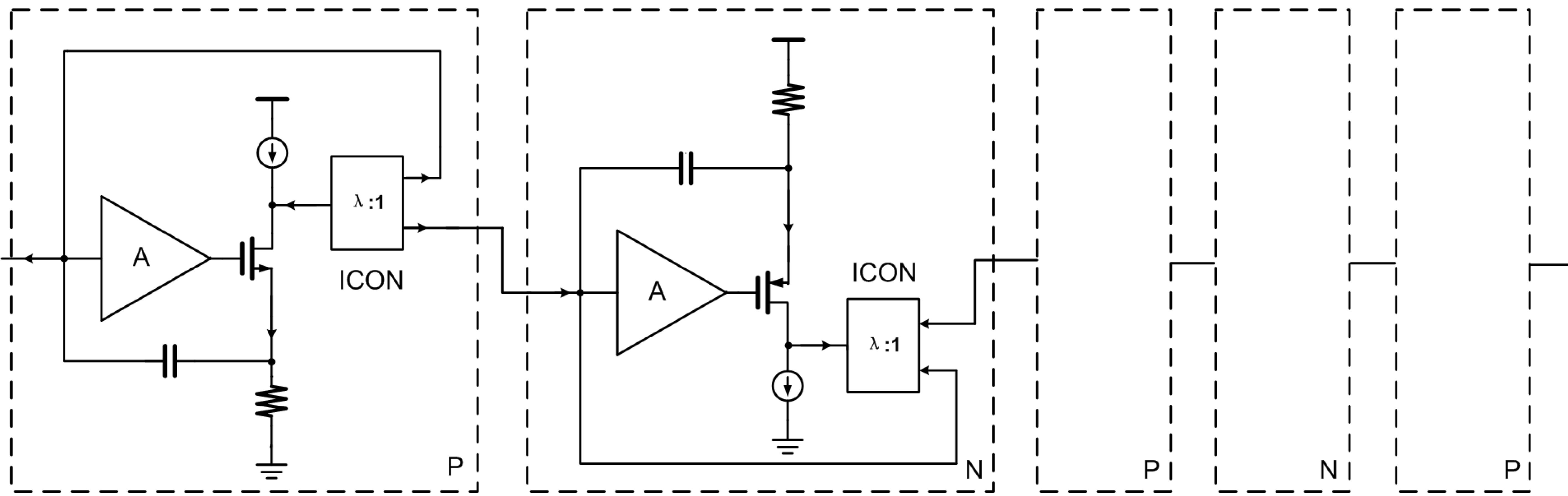

# 成形电路

# 4阶半高斯成形电路[2]

$$I_{out} = I_{in} \frac{1 + sRC}{1 + sRC(1 + \lambda)}$$

$$V_{out} = I_{in} \times \lambda R \frac{1 + sRC}{1 + sRC(1 + \lambda)}$$

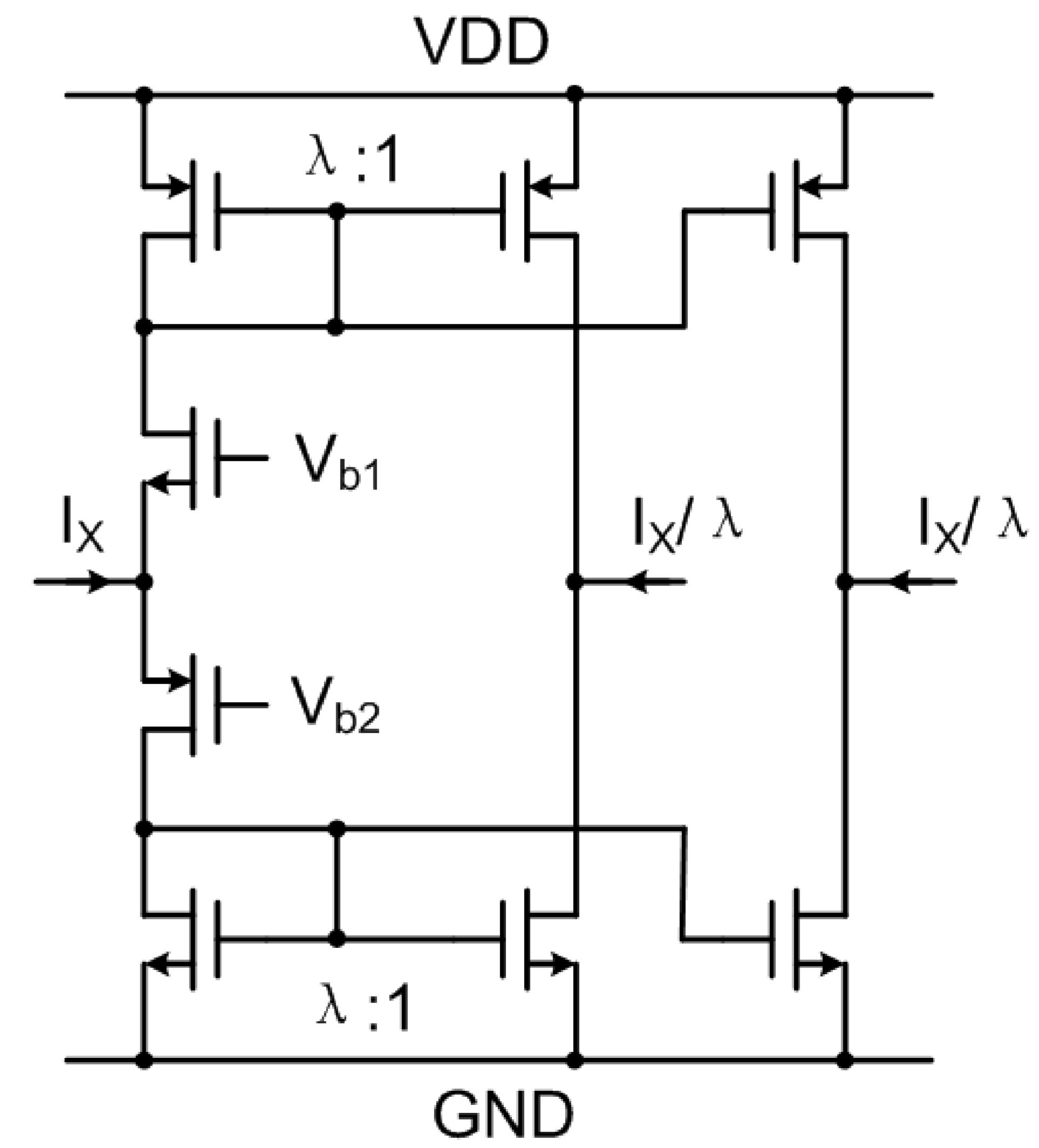

# ICON 单元电路

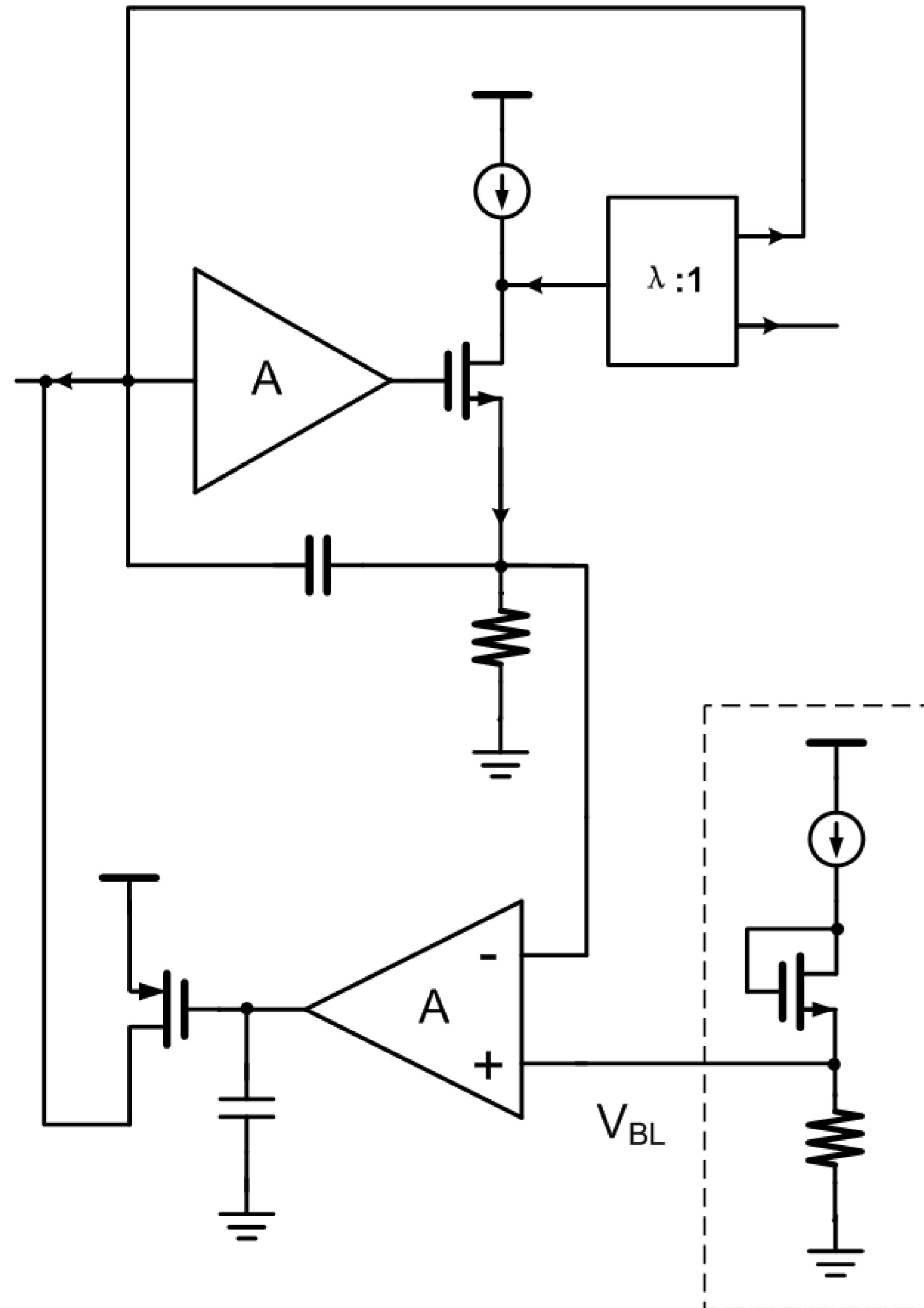

# 漏电流补偿电路

漏电流补偿电路原理图<sup>[3]</sup>

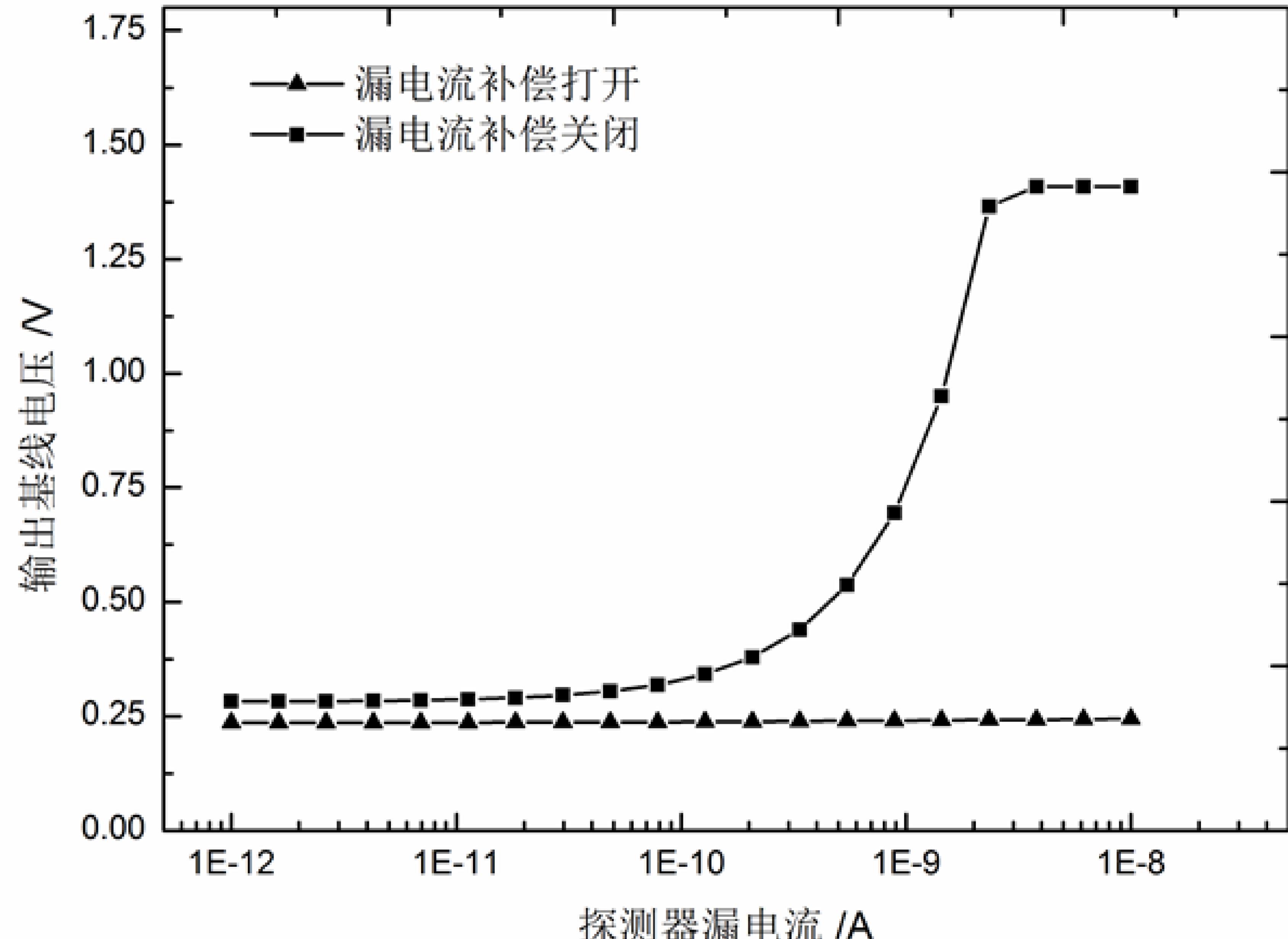

输出基线电压随漏电流变化的仿真结果

# 主要性能

表 1 CASACZT16 的基本性能指标

|       |                       |

|-------|-----------------------|

| 工艺    | Chartered 0.35μm CMOS |

| 增益    | 100、200、300、400mV/fC  |

| 达峰时间  | 1、1.3、2、4μs           |

| ENC   | 116e@4μs              |

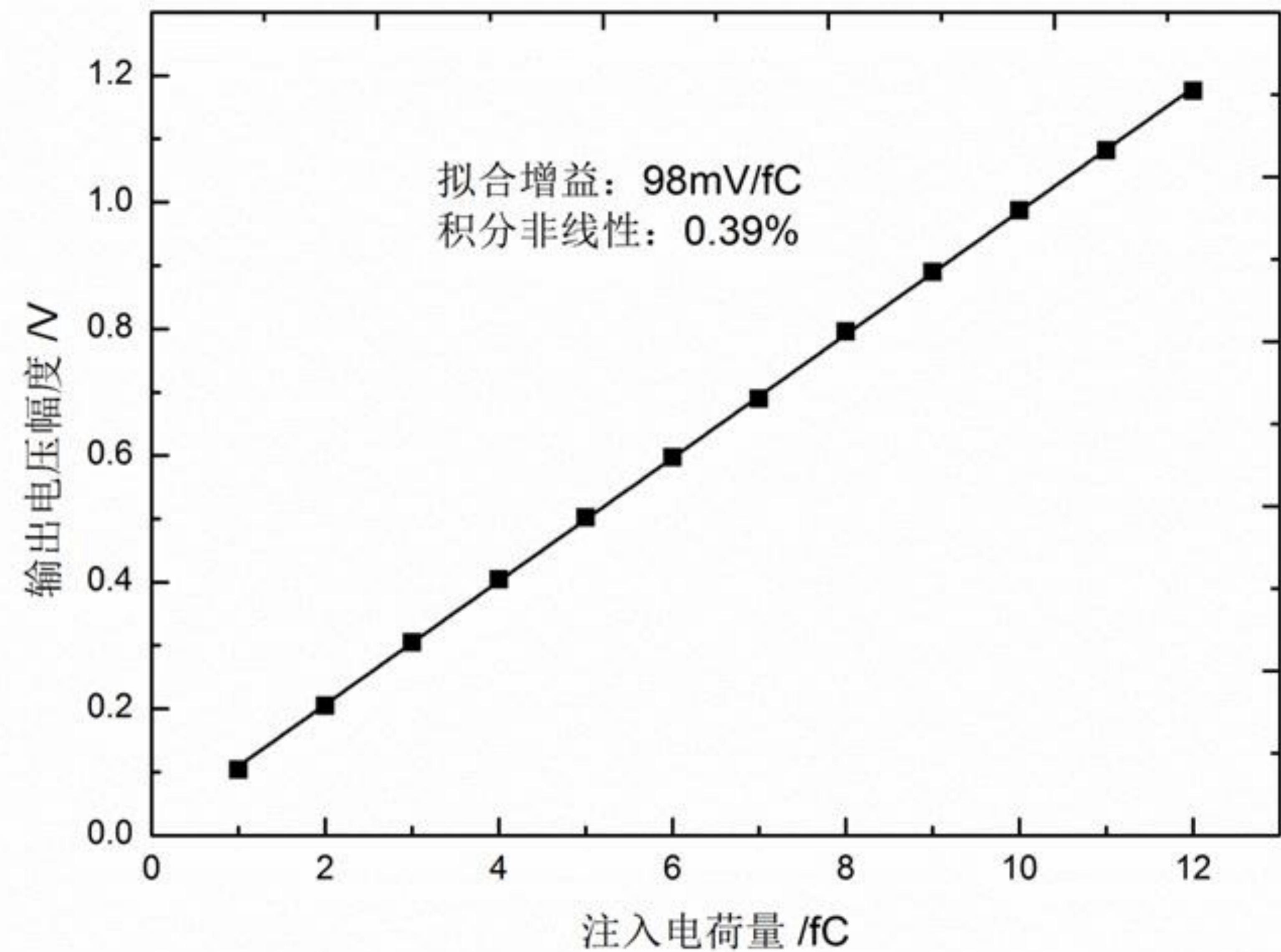

| 积分非线性 | 0.39%                 |

| 动态范围  | 360keV                |

| 功耗    | 7.3mW/通道              |

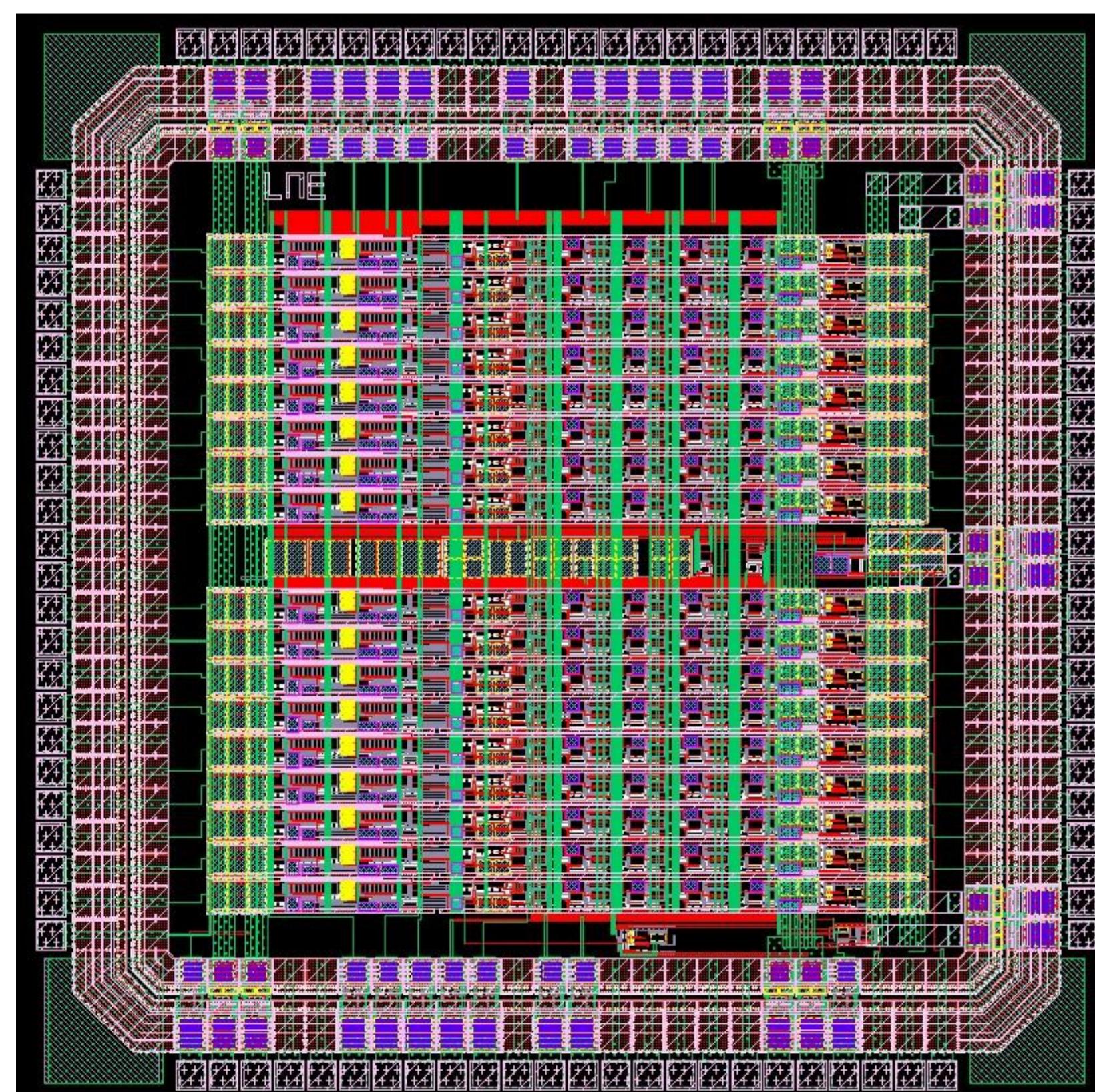

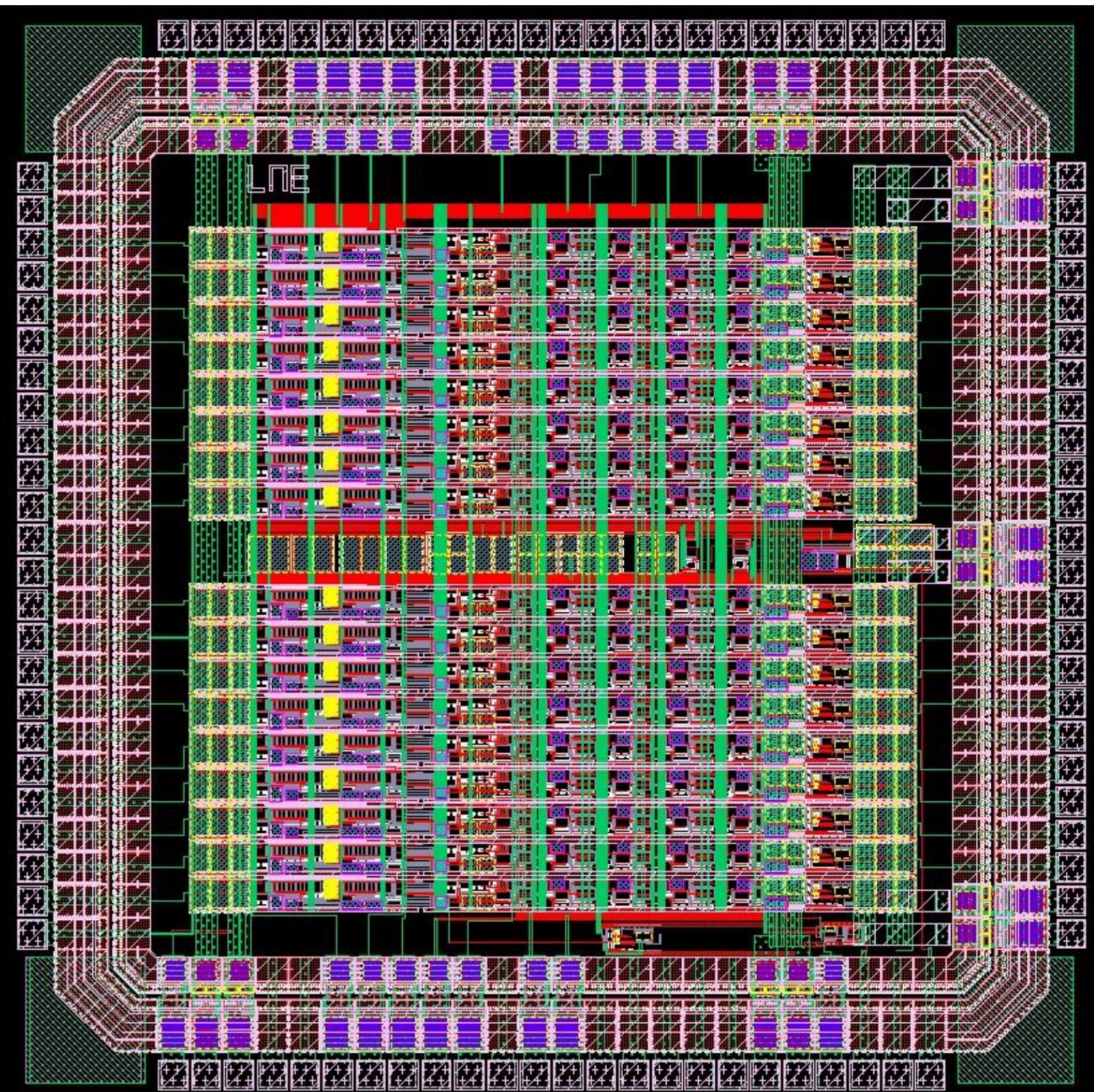

芯片版图

- 面积3mmX3mm

- 16通道+1测试通道

- 3.3V供电

- BGA封装

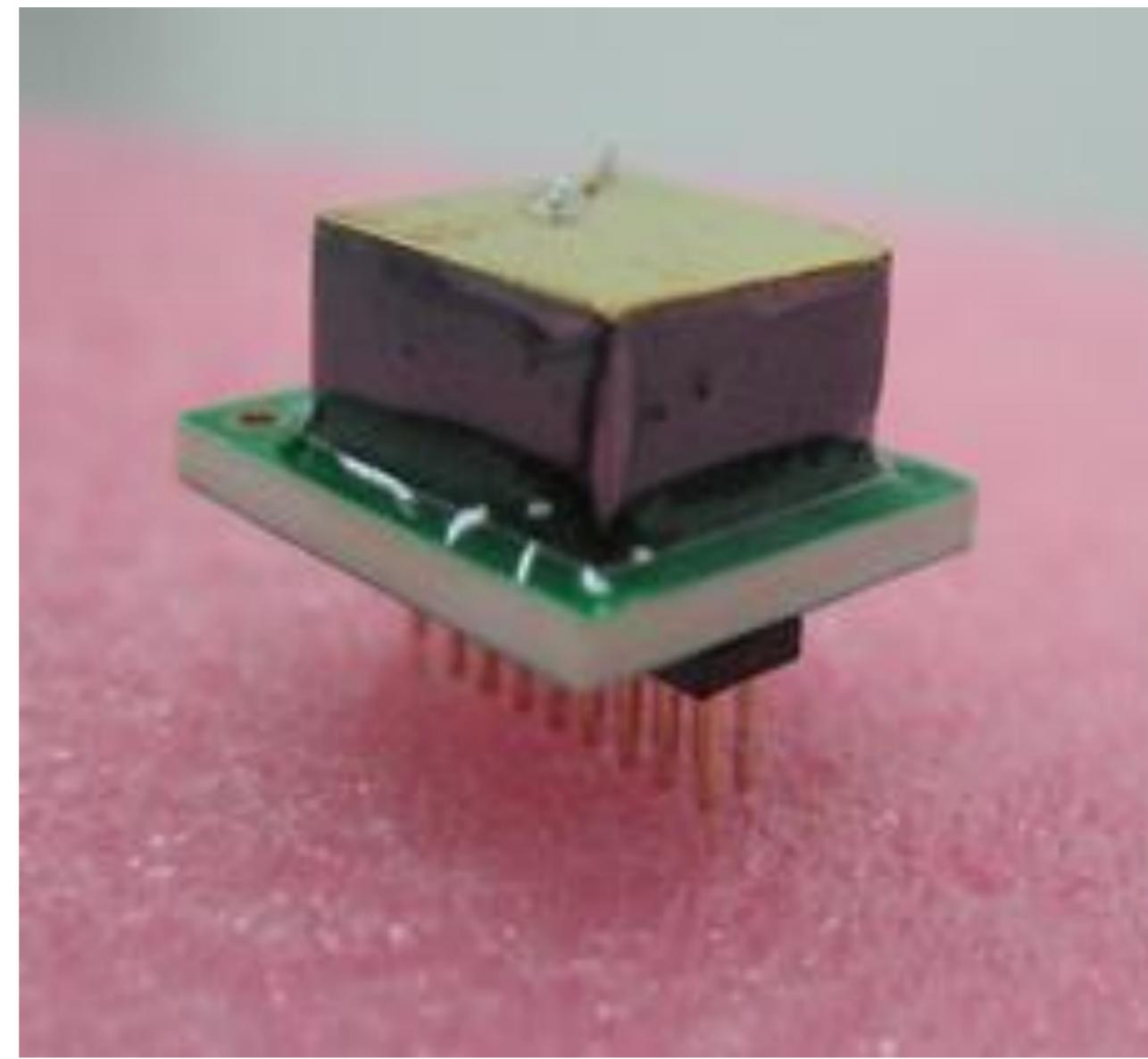

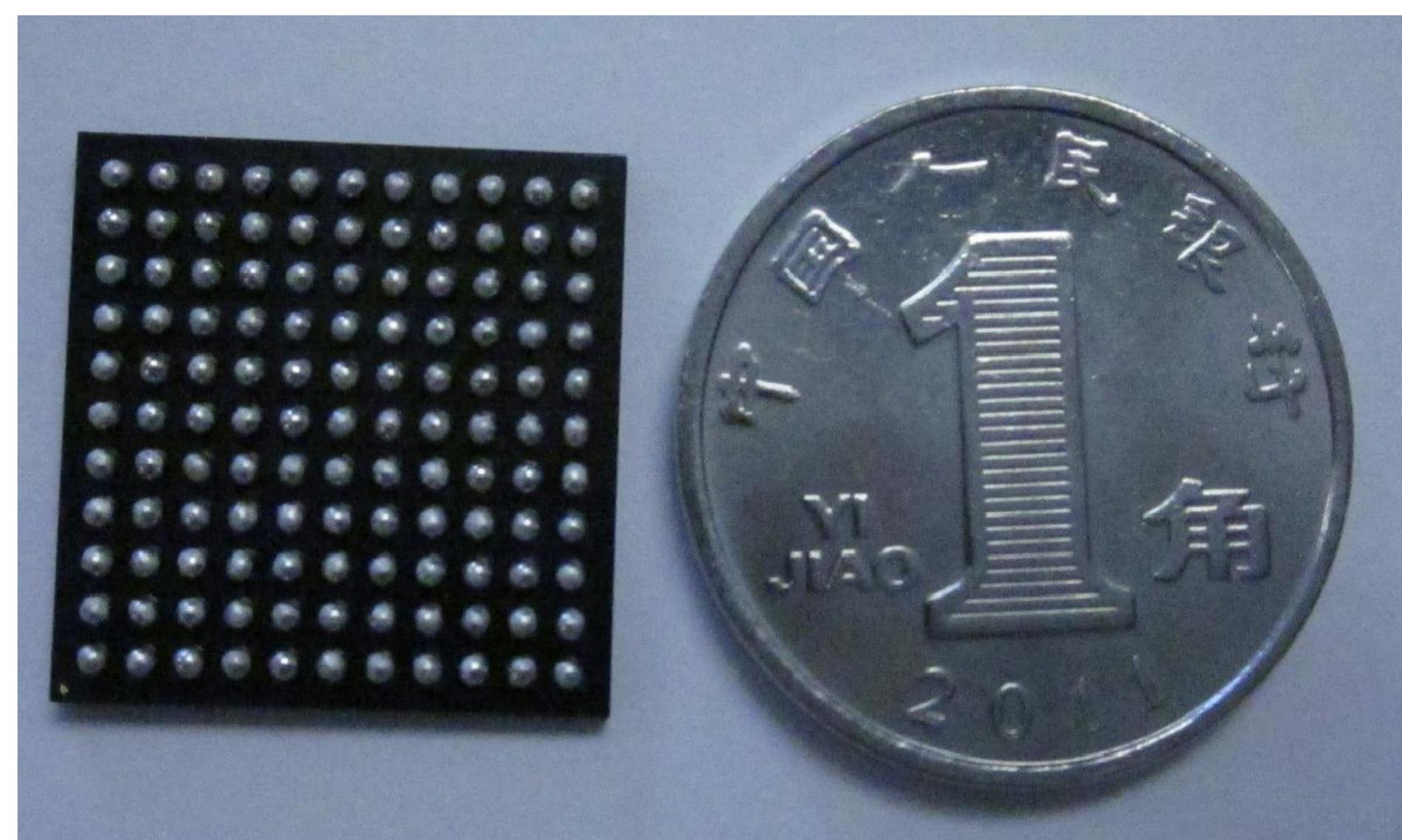

BGA封装的芯片

# 功能测试

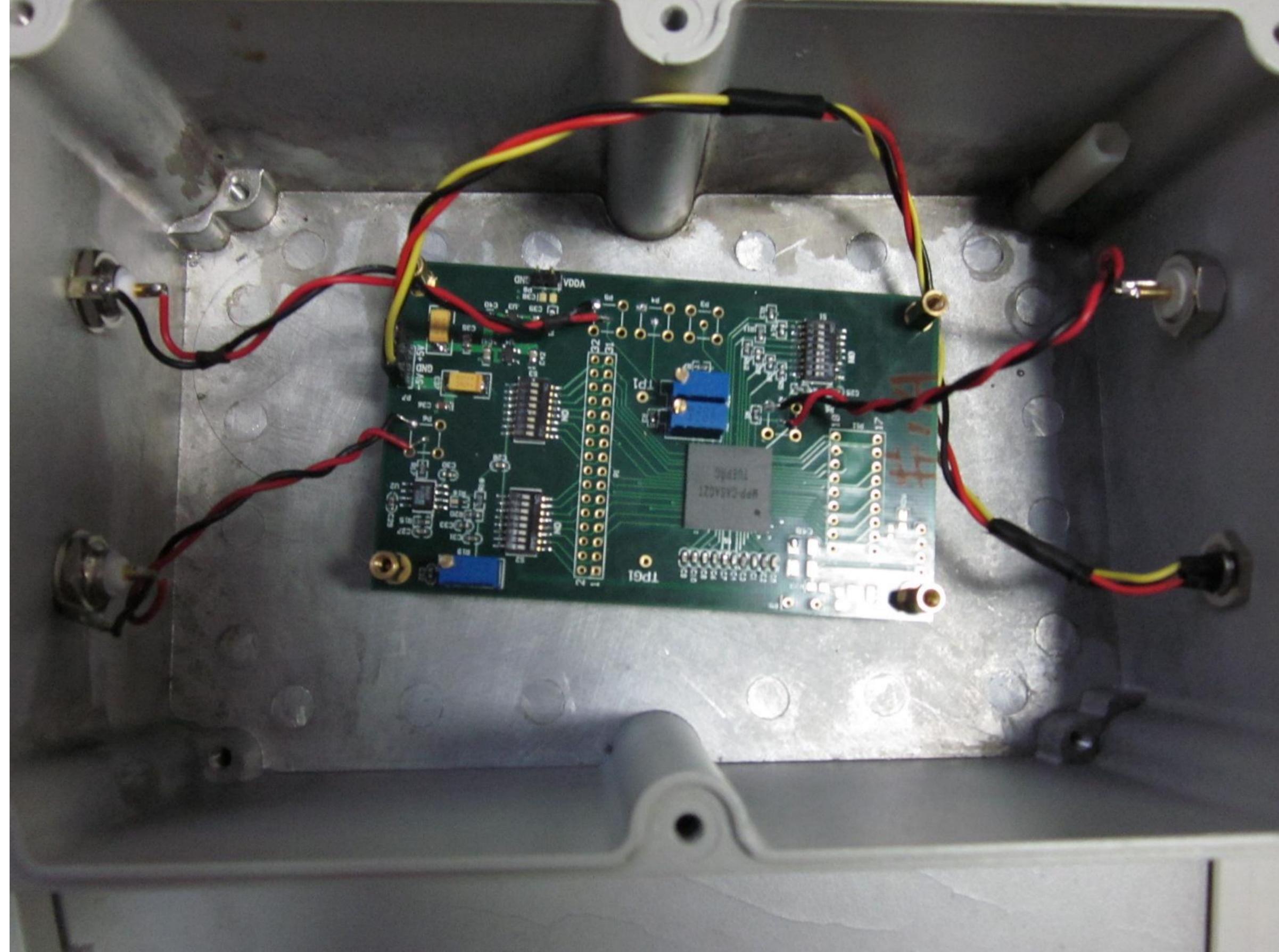

测试电路板

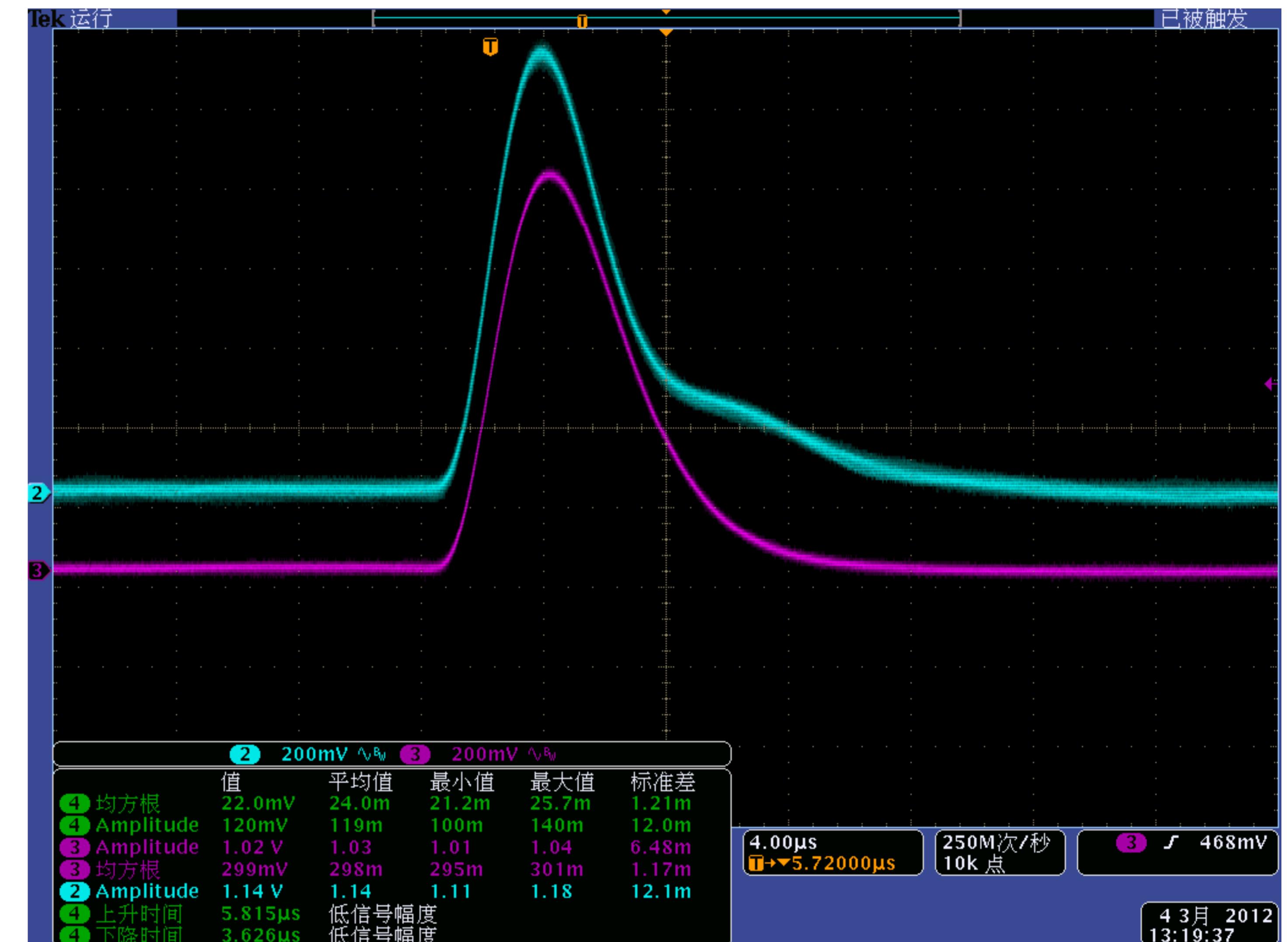

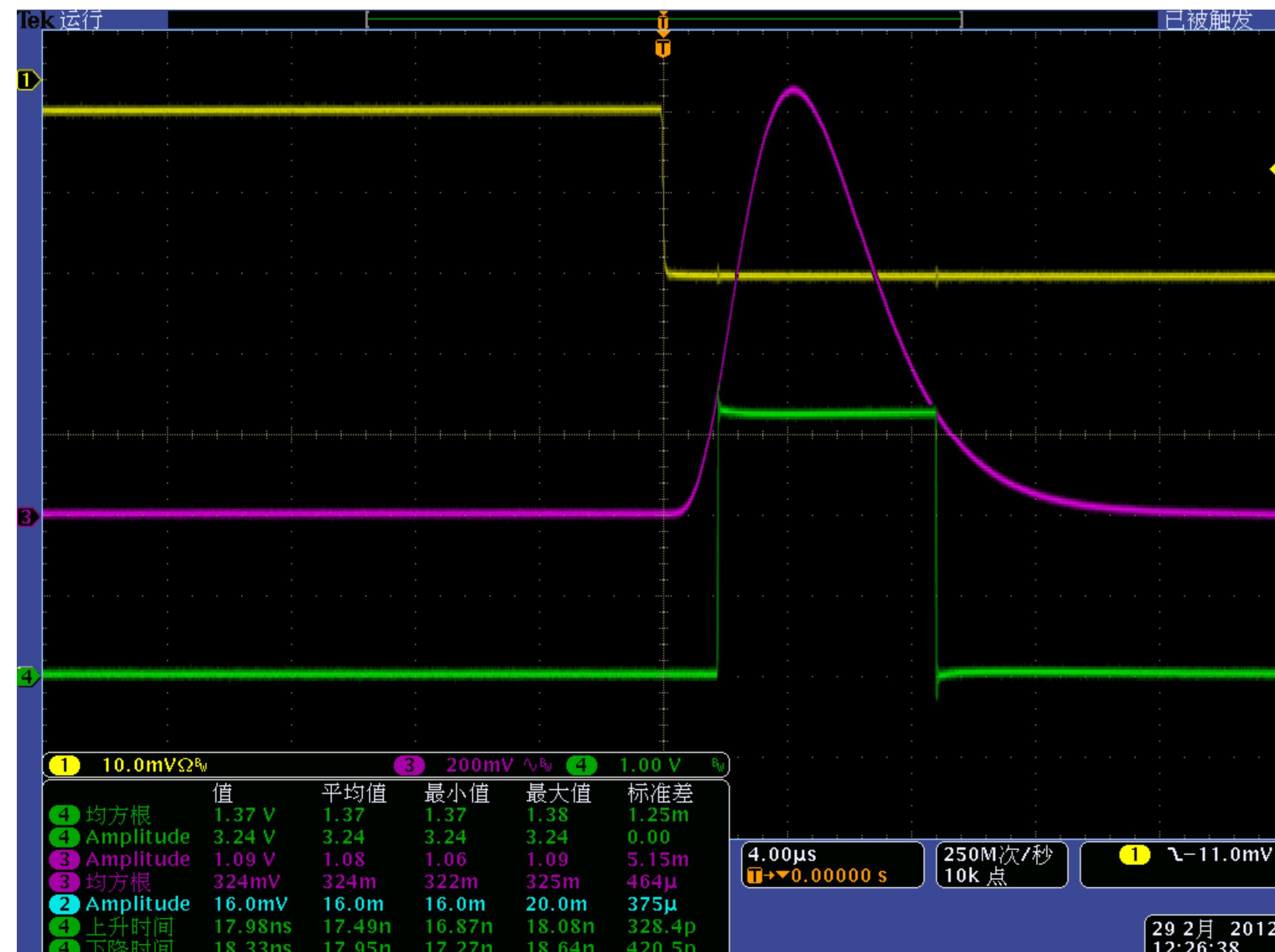

大增益时输出波形尾部畸变

芯片输入端的寄生电感效应

清华大学

Tsinghua University

# 线性测试

不同成形时间下的输出波形

输出电压与注入电荷的线性关系曲线

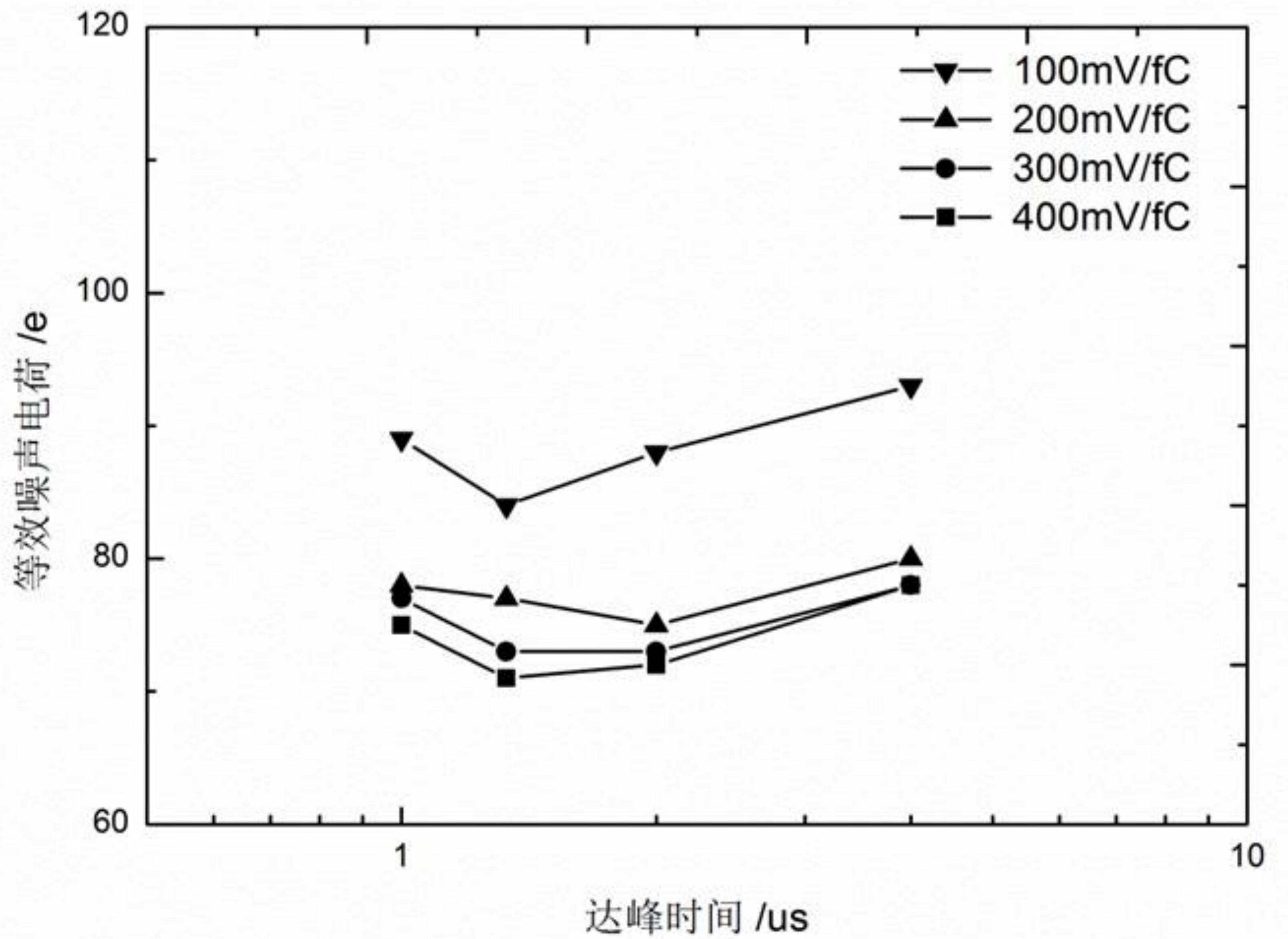

# ENC测试

不同增益等效噪声电荷随达峰时间的变化曲线

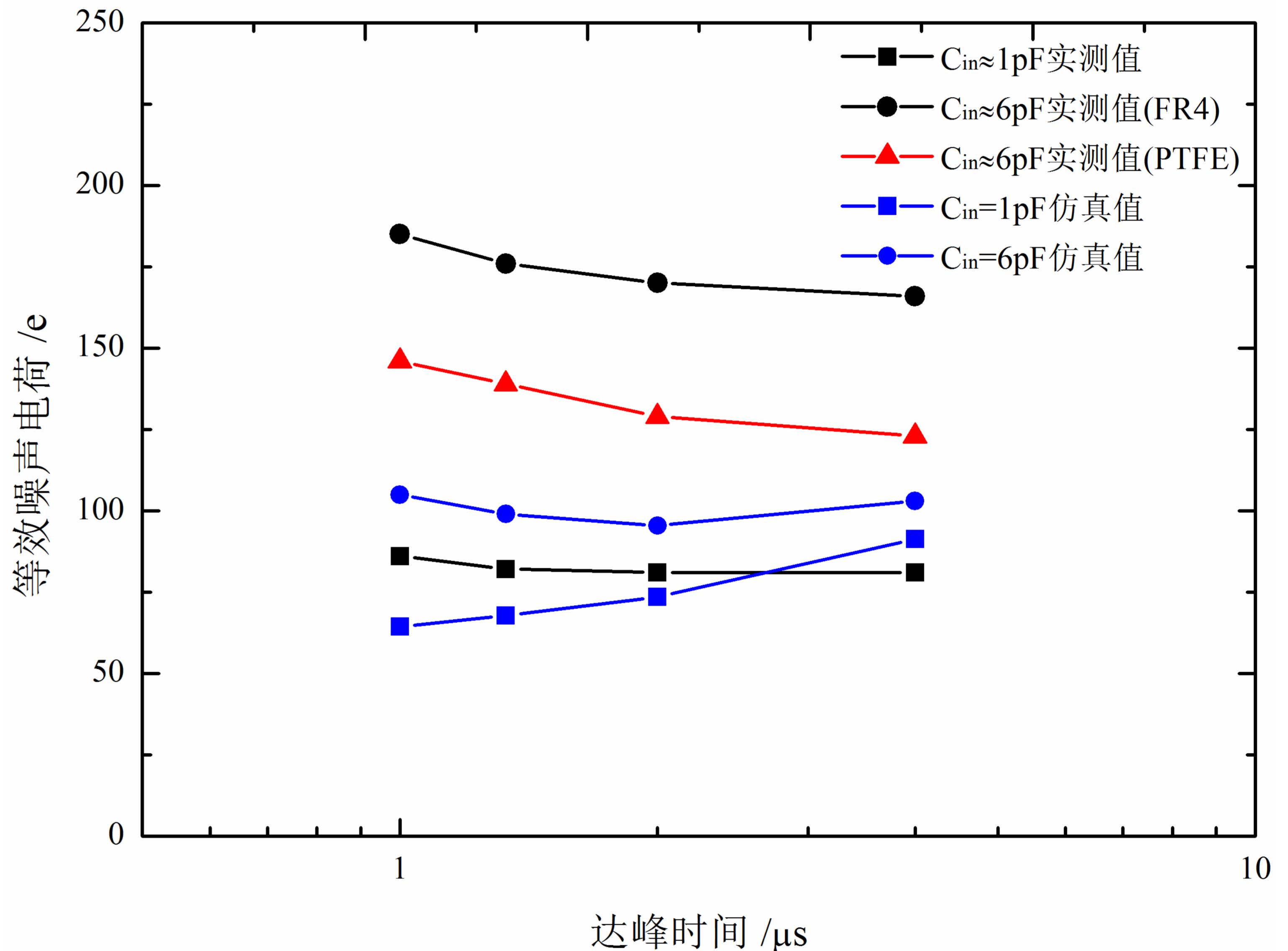

不同通道等效噪声电荷随达峰时间的变化曲线

- $C_{in}=1\text{pF}$ : 测试通道，输入端没有引出来

- $C_{in}=6\text{pF}$ : 普通通道，输入端连接到PCB上，封装寄生电容、PCB走线寄生电容使得输入电容增加为6pF

- 测试PCB板分别采用了FR4和PTFE两种板材

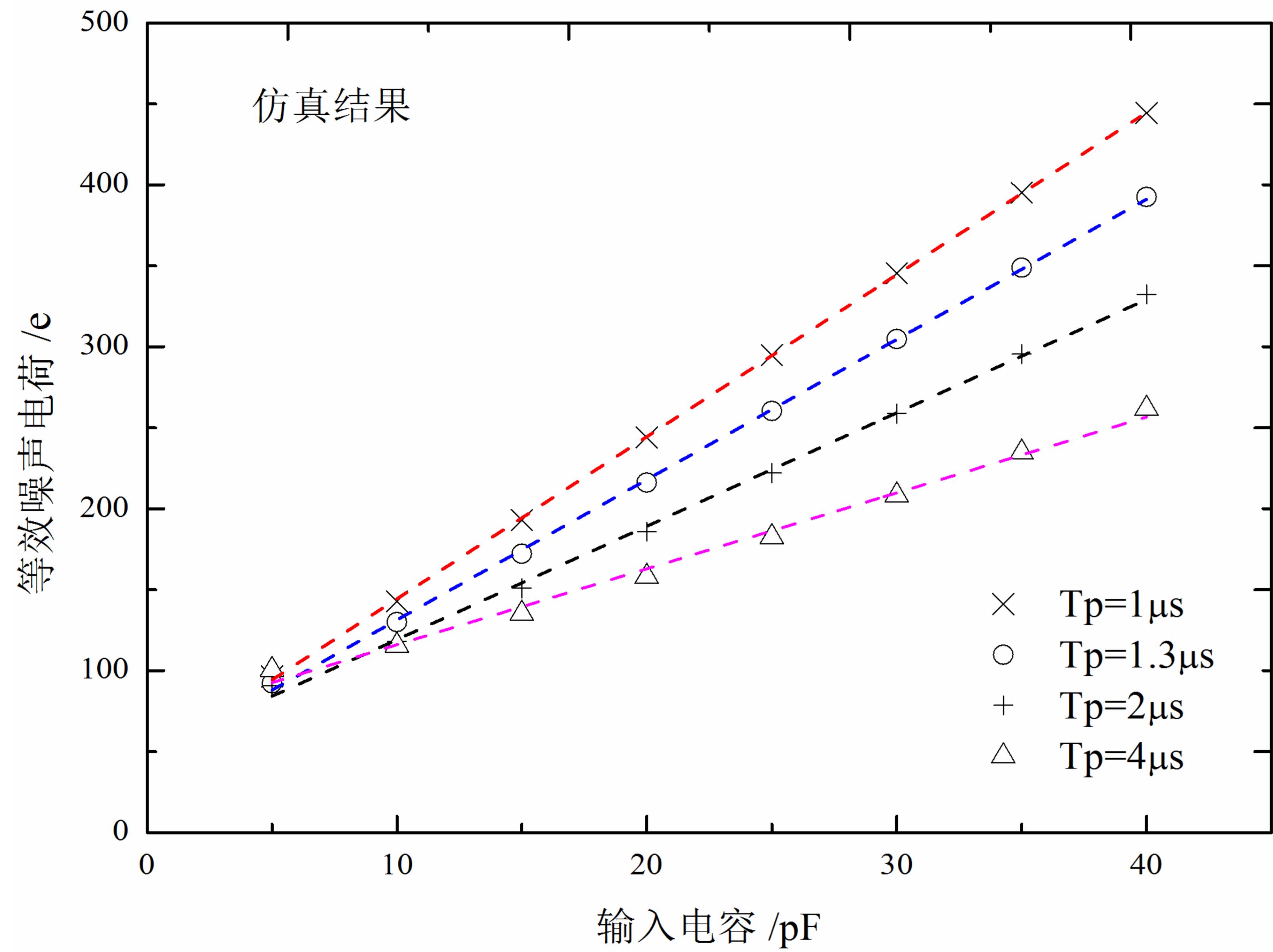

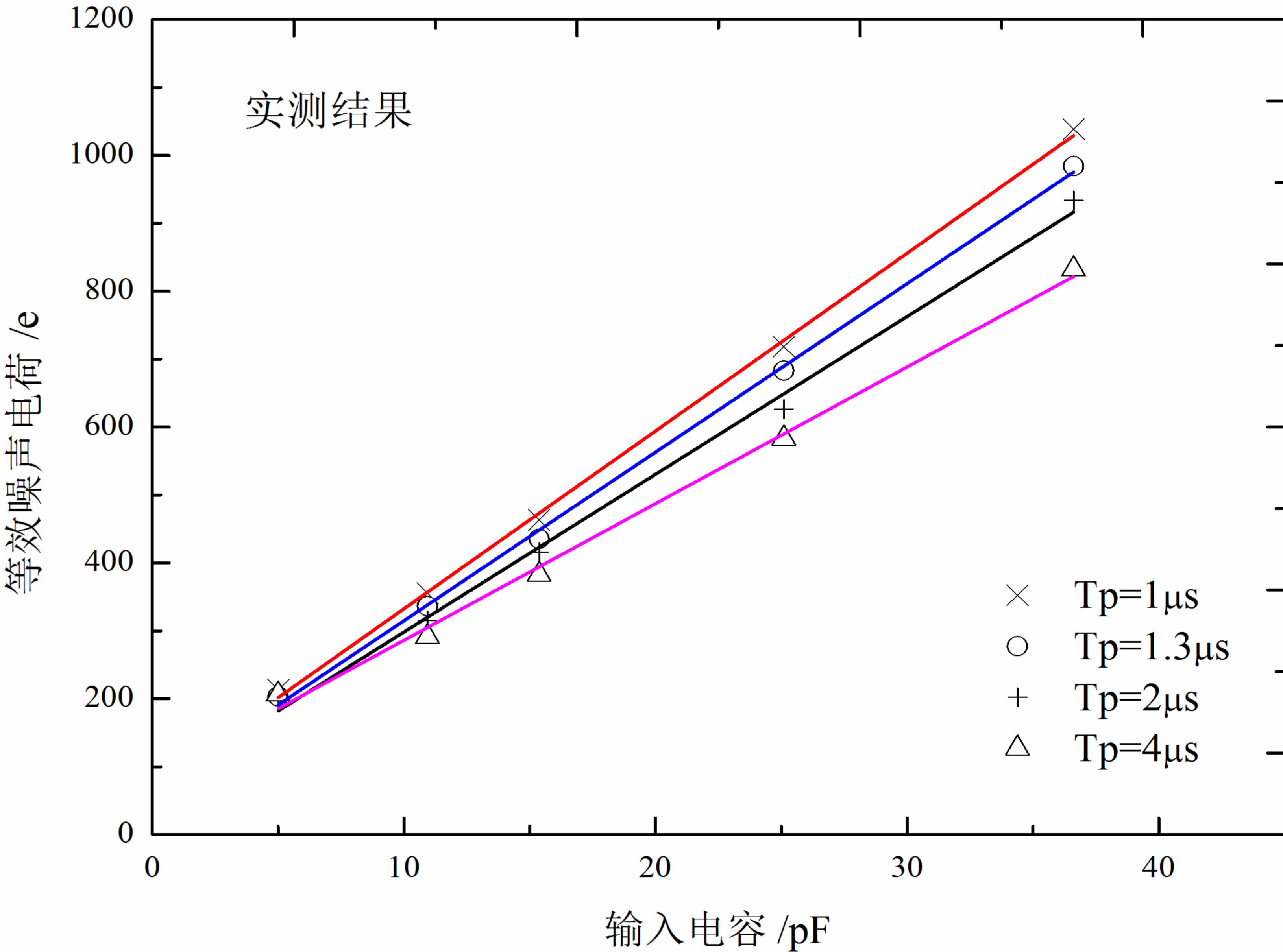

# 噪声斜率测试

不同达峰时间仿真得到的噪声电容斜率

仿真ENC:

44e+10e/pF@1us达峰时间

69e+4.7e/pF@4us达峰时间

不同达峰时间实测的噪声电容斜率

实测ENC:

71e+26e/pF@1us达峰时间

85e+20e/pF@4us达峰时间

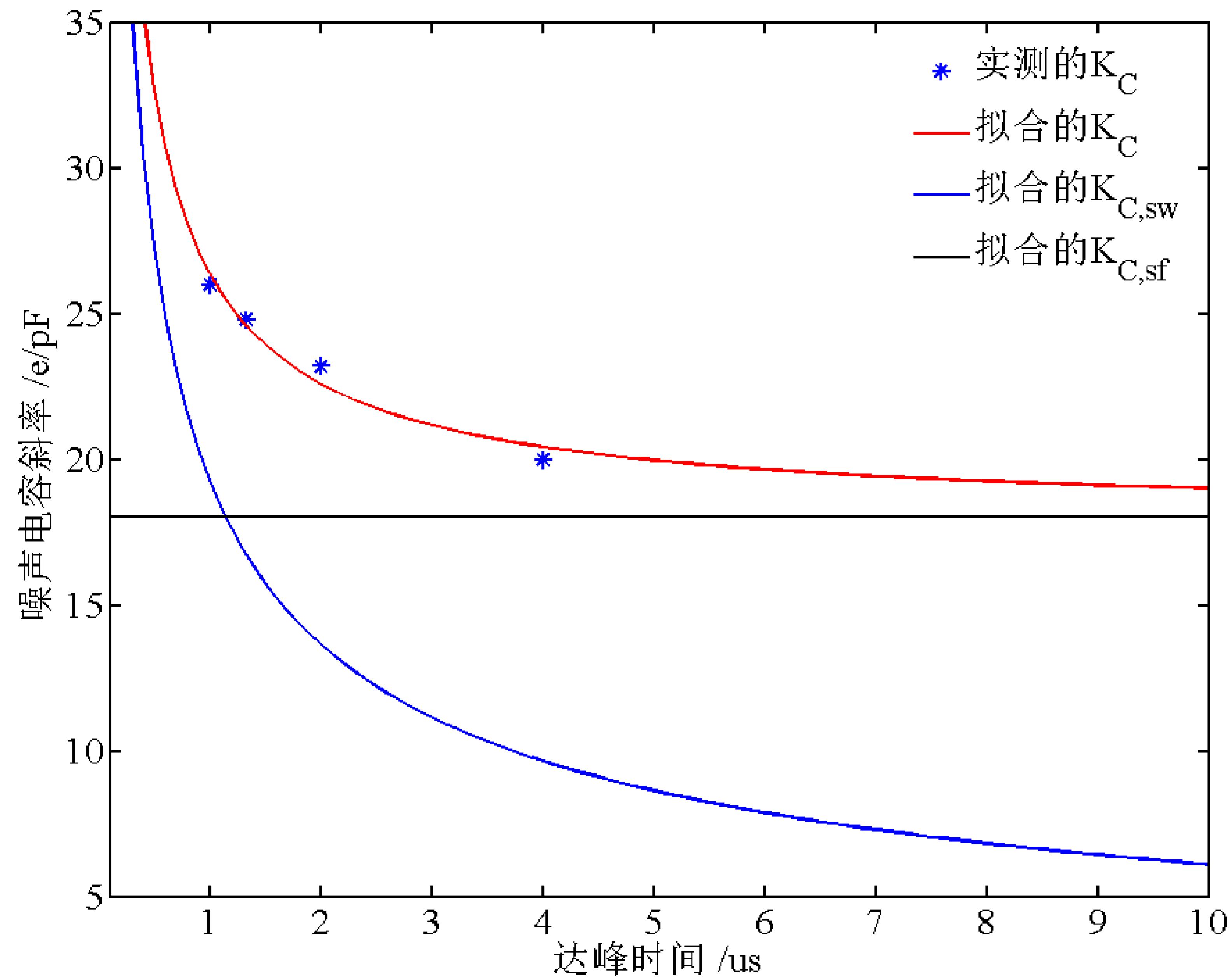

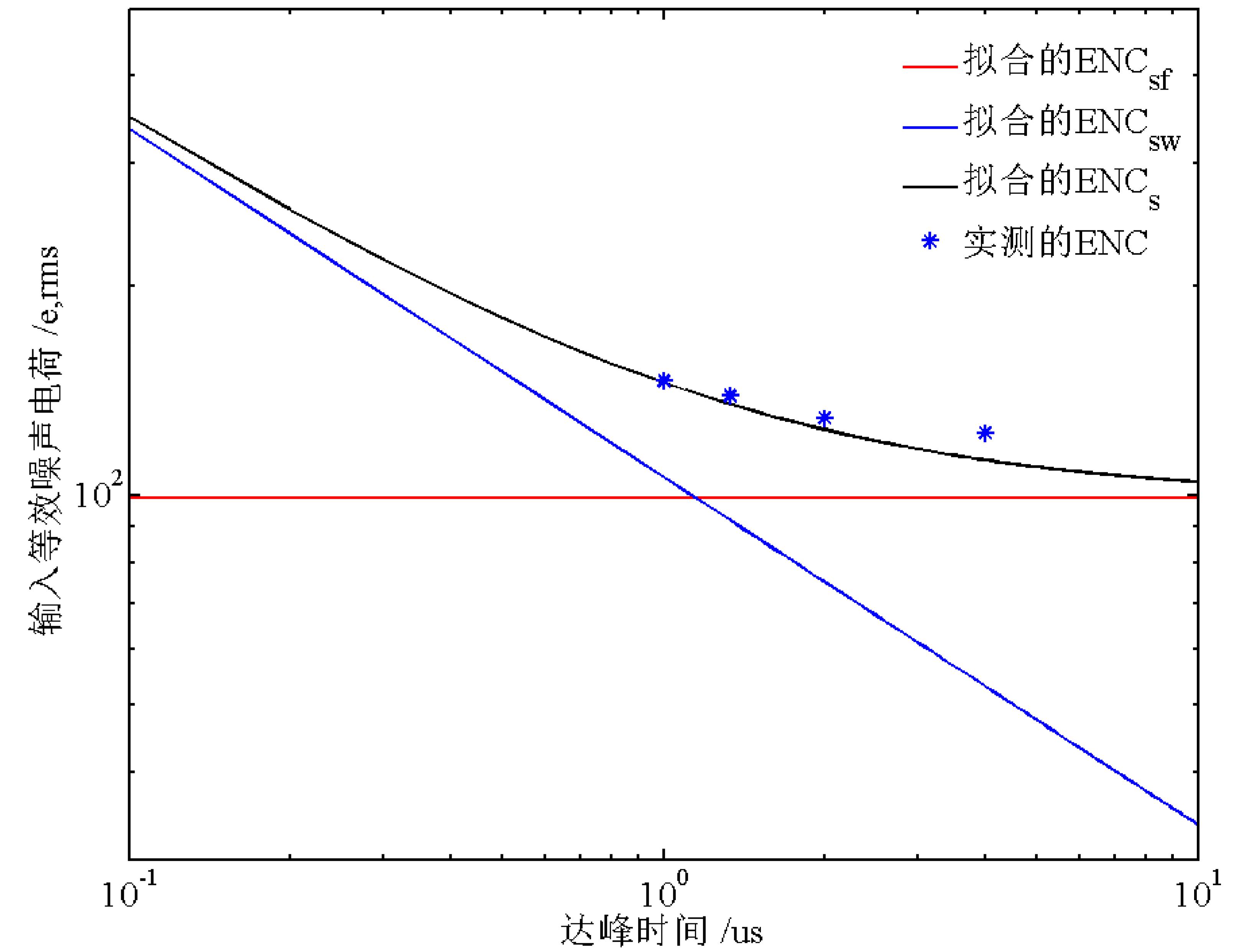

# 噪声斜率测试

噪声电容斜率随成形时间变化的拟合值

$$\text{噪声电容斜率公式: } K_C = \sqrt{\frac{a}{\tau_p} + b}$$

ENC随成形时间变化的拟合值

|     | $a$ ( $nV^2/Hz$ ) | $b$ ( $\mu V^2$ ) |

|-----|-------------------|-------------------|

| 仿真值 | 5.15              | 0.95              |

| 实测值 | 24.4              | 21.2              |

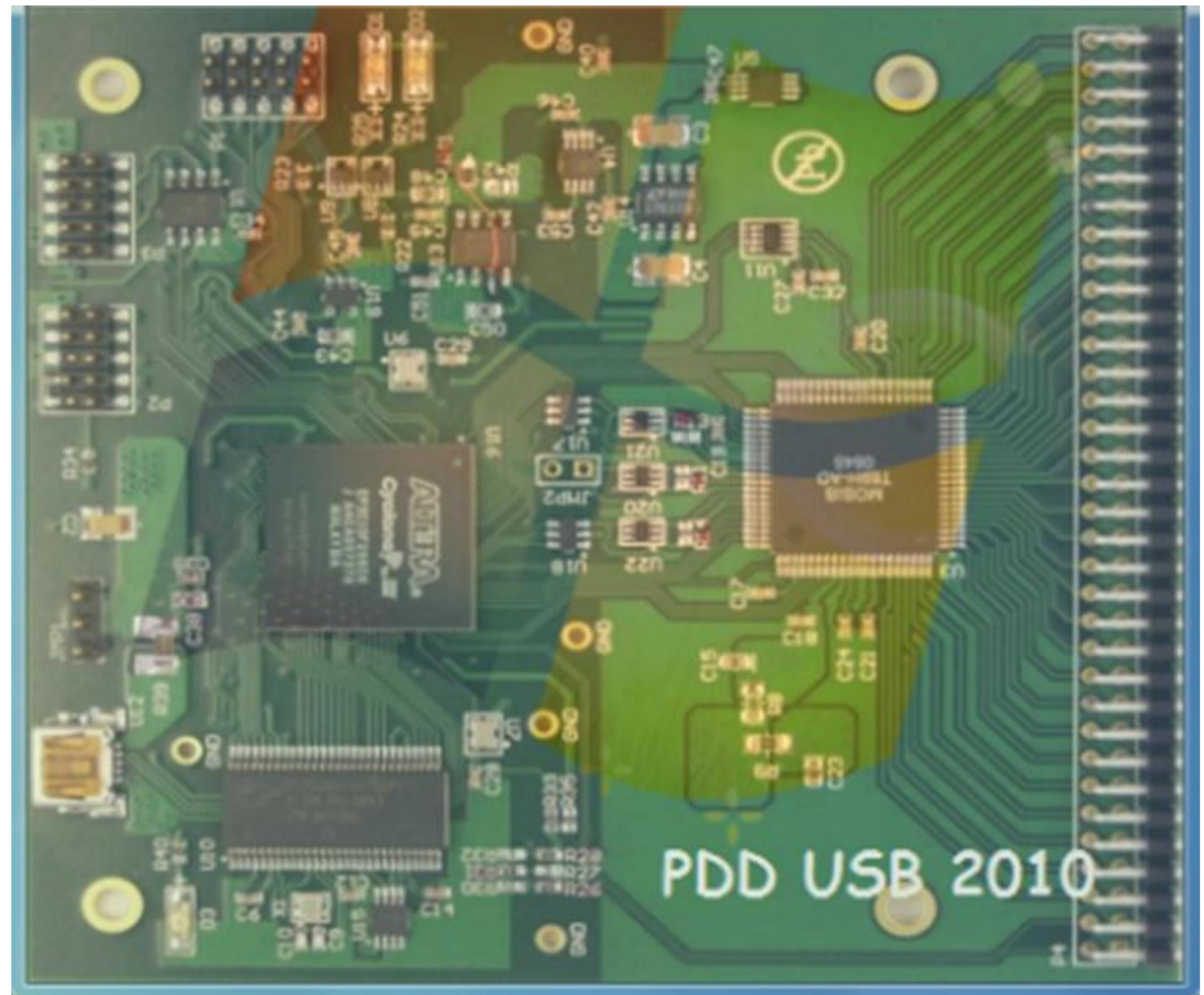

# PDD数据采集系统

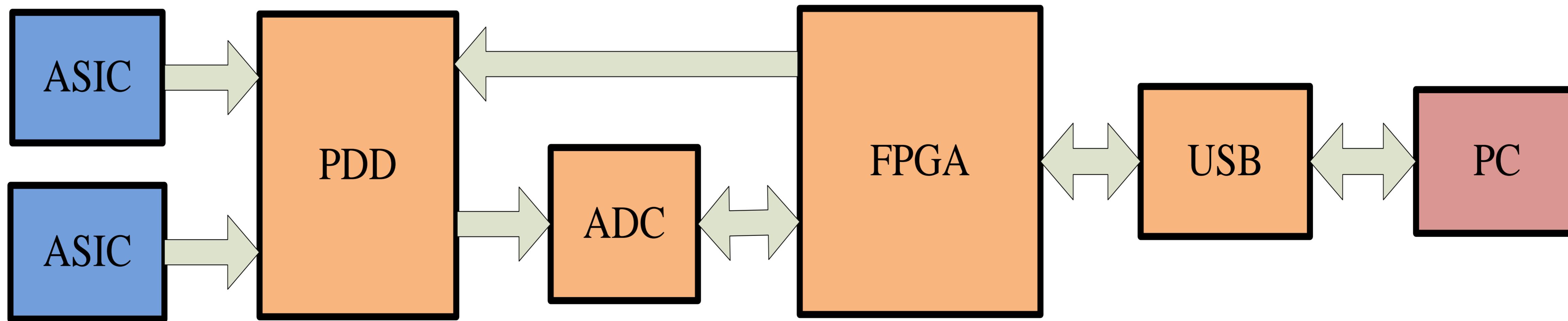

PDD USB数据采集板<sup>[4]</sup>

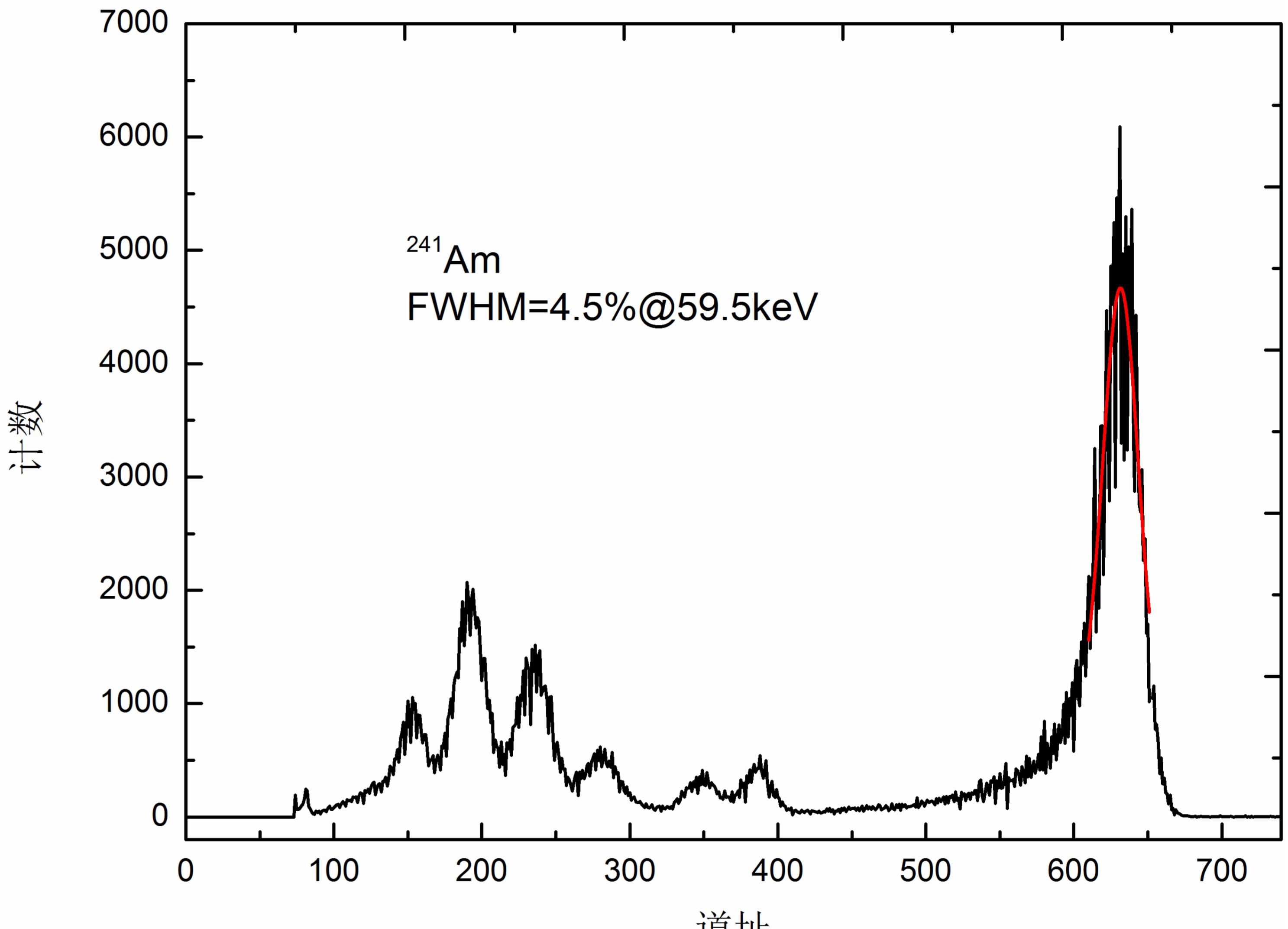

使用PDD数据采集板测得<sup>241</sup>Am的能谱图

32通道CdZnTe探测器能谱数据采集系统框图

# 总结及后续工作展望

- 设计了一款用于碲锌镉探测器信号读出的低噪声前端芯片，实现了前放、成形、漏电流补偿、甄别以及输出驱动放大等基本功能。

- 初步测试结果表明芯片各项功能均正常，基本达到了设计指标，满足应用需求。

- 6pF输入电容时测得的最小ENC为120e，测试通道测得的最小ENC为70e，1us和4us达峰时间测得的噪声斜率分别为26e/pF和20e/pF，实测结果比仿真结果偏大。

- 采用了PDD数据采集板搭建了一个32通道的数据采集系统，目前正在准备多通道的像素CdZnTe探测器，后续工作将使用该32通道数采系统对探测器进行性能评估和能谱测量。

# 参考文献

- [1] G. De Geronimo et al, “A CMOS detector leakage current self-adaptable continuous reset system: Theoretical analysis”, *NIMA*, 1999, 421:322-333.

- [2] C. Fiorini et al, “Integrated RC cell for time-invariant shaping amplifiers”, *IEEE TNS*, 2004, 51:1953-1960.

- [3] G. De Geronimo et al, “A CMOS baseline holder (BLH) for readout ASICs”. *IEEE TNS*, 2000, 47: 818-822.

- [4] G. De Geronimo et al, “Analog peak detector and derandomizer for high-rate spectroscopy”, *IEEE TNS*, 2002, 49: 1769-1773.

谢谢！

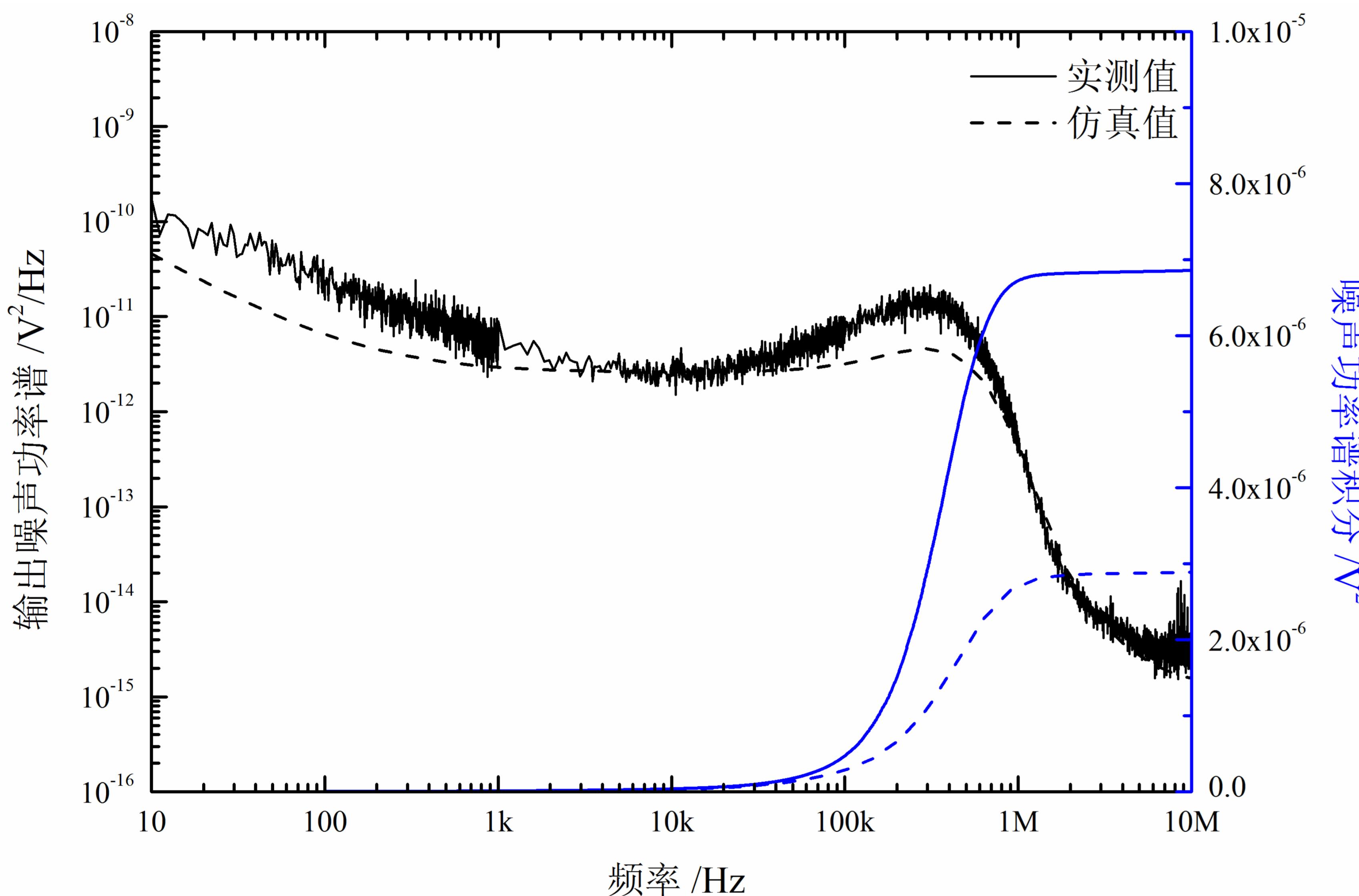

# 输出噪声功率谱分析

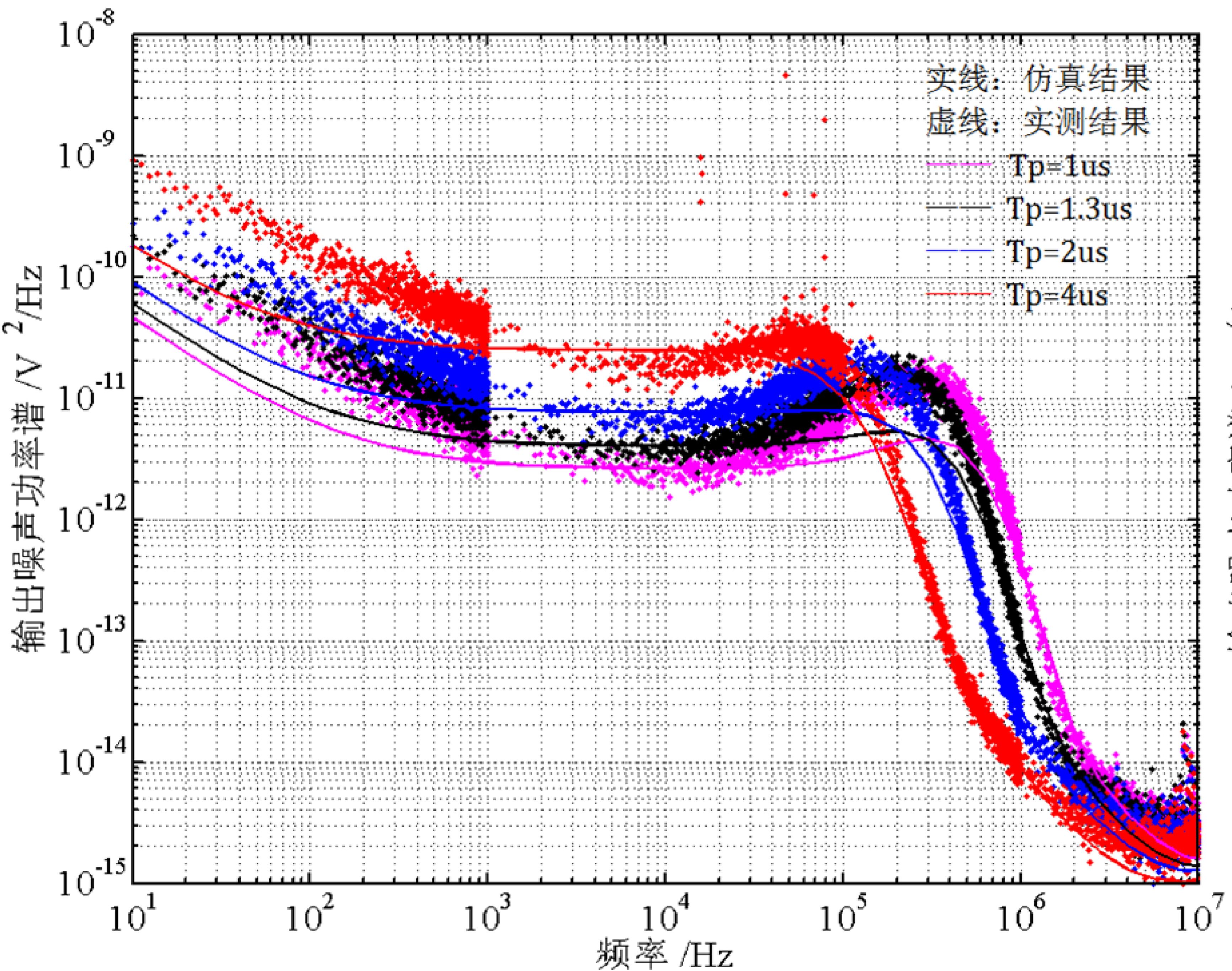

第5通道( $C_{in} \approx 6\text{pF}$ )输出噪声功率谱

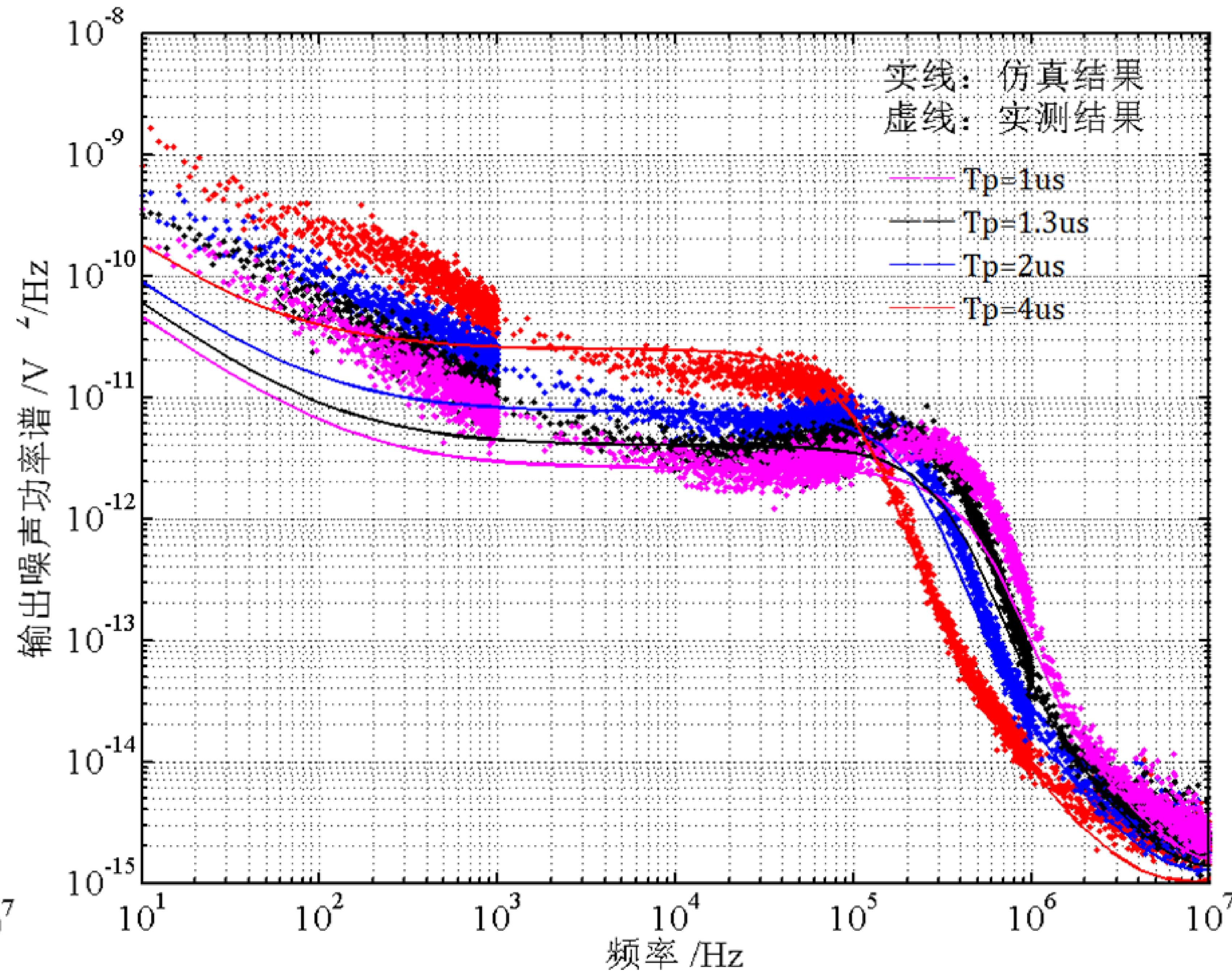

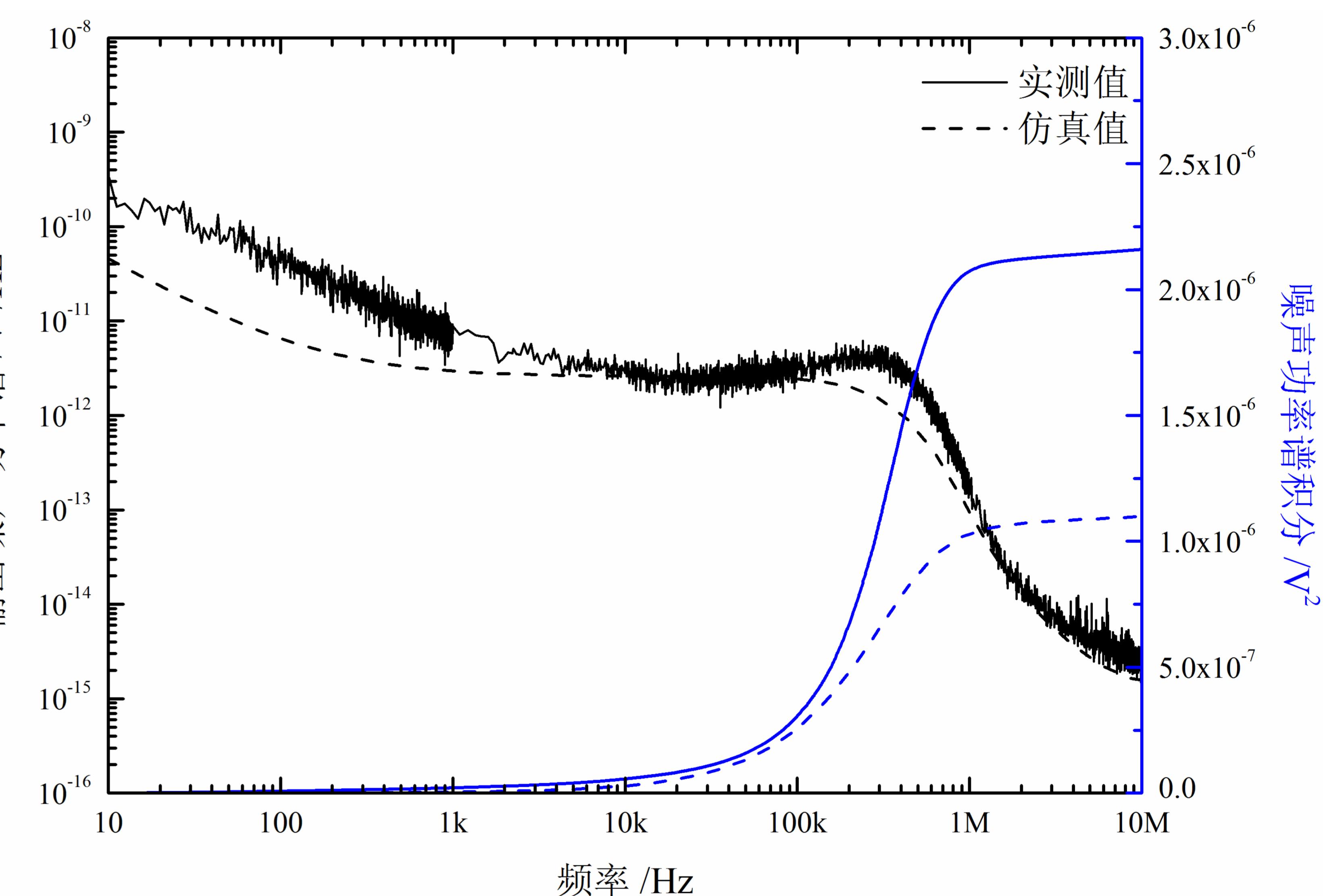

测试通道( $C_{in} \approx 1\text{pF}$ )输出噪声功率谱

# 输出噪声功率谱分析

第5通道( $C_{in} \approx 6\text{pF}$ )输出噪声功率谱

测试通道( $C_{in} \approx 1\text{pF}$ )输出噪声功率谱